Product Summary

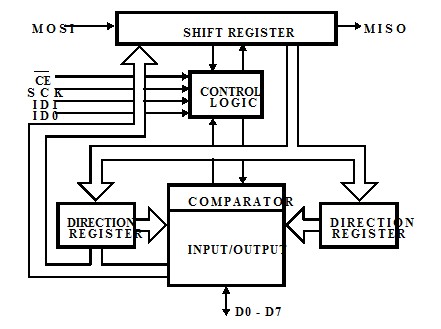

The CDP68HC68P1M is a serially addressed 8-bit input/output port that allows byte or individual bit control. It consists of three registers, an output buffer and control logic. The CDP68HC68P1M features a compare function that compares the data register and port pin values for 4 programmable conditions and sets a software accessible flag if the condition is satisfied. The user also has the option of bit-set or bit-clear when writing to the data register.

Parametrics

CDP68HC68P1M absolute maximum ratings: (1)DC supply voltage range(VDD): -0.5V to +7V; (2)Input voltage range, all inputs: -0.5V to VDD +0.5V; (3)DC input current, any one input: ±10mA; (4)Power dissipation per package(PD), TA=-40℃ to 60℃: 500mW; TA=60℃ to 85℃, derate linearly at: 12mW/℃ to 200mW; TA=-40℃ to 60℃: 300mW; TA=60℃ to 85℃, derate linearly at: 5mW/℃ to 175mW.

Features

CDP68HC68P1M features: (1)Fully static operation; (2)Operating voltage range 3-6V; (3)Compatible with intersil/motorola SPI bus; (4)2 external address pins tied to VDD or VSS to allow up to 4 devices to share the same chip enable; (5)Versatile bit-set and bit-clear capability; (6)accepts either SCK clock polarity-SCK voltage level is latched when chip enable goes active; (7)All inputs are schmitt-trigger; (8)8-bit I/O Port-each bit can be individually programmed as an input or output via an 8-bit data direction register; (9)Programmable on board comparator; (10)Simultaneous transfer of compare information to CPU during read or write-separate access not required.

Diagrams

|

CDP6402 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

CDP6402C |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

CDP6805E3E |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

CDP6872 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

CDP68HC68A2 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

CDP68HC68P1 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))